# TE 光电阴极制作技术的研究

中国科学院西安光学精密机械研究所

半导体光电器件研究室 (西安 710068)

李相民 侯洵 程军 王存让

摘要 对 TE 光电阴极制作工艺中存在的肖特基结热退化现象以及为了实现 TE 阴极器件化,设计了超高真空激活系统和制作工艺流程,并采用 PECVD-Si<sub>3</sub>N<sub>4</sub> 绝缘膜和多次蒸银方法彻底消除了热退化现象,从而实现在真空系统内场助电极的原位连接和阴极的激活,为实现 TE 光电阴极器件的分离打下基础。

关键词 肖特基结 TE 阴极 PECVD-Si<sub>3</sub>N<sub>4</sub> 热退化 Ag 膜

### 1 引言

由于 NEA (Negative Affinity)光电阴极的长波阈值被限制在  $1.1\mu\text{m}^{(1)}$ ,为了突破这个极限,1974 年 Bell 等人首先提出了转移电子 (Transferred Electron,TE)阴极并在实验上实现了光电发射<sup>(2)</sup>。之后,伴随着液相外延(LPE) 技术的不断成熟和带隙可调的 In-GaAsP 合金的应用,在理论研究和制作工艺方面,TE 光电阴极迅速发展起来。具有双异质结的 Ag/p-InP/p-InGaAsP/InP 阴极被认为最具有应用前景,它的红外吸收波长已展到  $2.0\mu\text{m}^{(3)}$ 。1981 年 Escher 等人利用双异质结阴极首次实现了  $0.9\sim1.6\mu\text{m}$  的光电成象,并获得了  $20\sim22\text{c}/\text{mm}$  的空间分辨率<sup>(4)</sup>。

尽管 TE 阴极在实研室内实现了光电成象,但分析 TE 阴极的结构特征,并与 NEA 阴极相比较,要制作具有 TE 阴极的独立光电器件,还存在许多困难,其中在真空系统内一次完成场助电极的连接、激活和器件分离是最主要困难之一。如果不能实现场助电极的原位连接和激活,而是打开真空系统,就会引起 TE 阴极至今不能实现器件分离的主要原因之

针对这些问题我们设计了超高真空激活系统,并提出应用 PECVD (Plasma Enhance Chemical Vapor Deposition) 技术生长的 Si<sub>3</sub>N<sub>4</sub> 绝缘膜和多次蒸银方法解决了场助引线原位连接的困难。本文将对工艺中的困难、解决方法

和实验结果作较详细的论述。

2 TE 阴极制作工艺中的困难

图。显然,在蒸银制备肖特基结之后,无法在真空系统外给肖特基结施加场助电极,必须打开真空系统,进行场助电极连接和其它激活前准备工作。这期间,由于暴露于大气,肖特基结银表面必然受到污染,当装入真空系统后,必

图 1 给出了 TE 光电阴极的制作工艺流程

准备工作。这期间,由于暴露于大气,肖特基结银表面必然受到污染,当装入真空系统后,必须经过烘烤才能达到要求的超高真空度,而且在激活前还要在550℃的温度下进行短时间的

表面热清洁。真空系统的烘烤和表面热清洁会

阴极材料的生长 →欧姆接触的制备→ 装入超高真空 系统

撒活前准备 ← 肖特基结制备 ← 真空系统烘烤及 表面热清洁

\* 表面二次热清洁及→ 光电阴极的激活 → 光谱灵敏度测定 真空系统的烘烤 → 光电阴极的激活 → 光谱灵敏度测定

> 图1 TE光电阴极制备工艺流程 半导体技术 1995年8月第4期

26

造成肖特基结特性的严重劣化,甚至失去整流 特性<sup>⑤</sup>,从而导致阴极失效。

可见,要想消除肖特基结热退化现象,只有在肖特基结制备之后,在不打开真空系统的前提下,完成场助电极的原位连接和其它各项激活前的准备工作,同时要求真空系统和新工艺能够和制备分立 TE 阴极器件的工艺相兼容,为制作独立的 TE 阴极光电器件做准备。综合上述考虑,我们设计了超高真空激活系统和新的工艺流程。

#### 3 解决方法

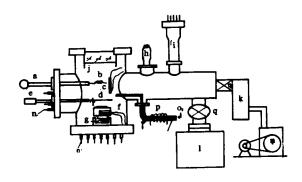

我们利用 PECVD-Si<sub>3</sub>N<sub>4</sub> 绝缘膜和多次蒸银工艺来解决上述问题,其基本思想是: 阴极放入真空系统之前,把场助电极键合于阴极表面的非有源区,并通过绝缘膜与阴极隔离开来,在真空系统内通过第一次蒸银膜完成肖特基结制备后,再进行第二次蒸一层厚银膜,使场助电极与有源区桥连起来,从而实现在真空系统内场助电级的连接,为此,我们设计具有可移动掩模板的超高真空激活系统,如图 2 所示。下面对这个工艺流程作进一步说明。

图 2 场助阴极超高真空激活系统

a 推拉杆;b 蒸银钨丝;c 铯离子源;d 挡板;e 螺旋游标;f 热电阻;g 热子;h 高真空规管;i 四极质谱仪;j 石英玻璃视窗;k 分子筛;l 溅射离子泵;m 机械泵;n 电极;o 银管;p 加热丝;q高真空阀;r 阴极外延片

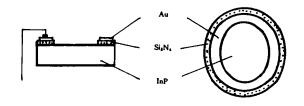

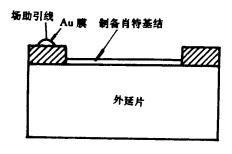

在外延片表面上的非有源区部分先生长一层 PECVD-Si<sub>3</sub>N<sub>4</sub> 绝缘膜,厚度大约为 100nm。在 Si<sub>3</sub>N<sub>4</sub> 膜上镀几个直径为 1~2mm,厚度大于1µm 圆形金膜,作为场助电极的键合点(多镀半导体技术 1995 年 8 月第 4 期

几个是为了键合时备用),然后,用超声键合工 艺把场助电极与金膜连接起来,如图 3 所示。键 合要求金膜要有足够的厚度,而且与 Si<sub>3</sub>N<sub>4</sub> 膜 的粘附要牢固,否则键合不牢或键合不上,因 此,淀积金膜之前,Si<sub>3</sub>N<sub>4</sub>膜表面要经过严格清 洗。Si<sub>3</sub>N<sub>4</sub> 膜是作为金膜与外延片之间的隔离 膜,至少应当具有大于 10V 的击穿电压,因此, 它的膜厚通常应大于 100nm。当完成上述工艺 后,把阴极放入真空系统,阴极要经过长时间 270℃左右的热烘烤和大约550℃的短时间表 面热清洁过程,因此要求 Si<sub>3</sub>N<sub>4</sub> 膜/InP 界面要 具有良好的耐热处理特性,实验表明 PECVD-Si<sub>3</sub>N<sub>4</sub> 膜能够满足上述要求<sup>(6)</sup>。此外,之所以选 择 PECVD 技术制备的 Si<sub>3</sub>N<sub>4</sub> 膜作为隔离膜, 是因为 PECVD 的生长温度只有 300 C左右, 在这样低的温度下,不会对外延片表面造成热 损伤。

图 3 放入真空系统之前阴极结构示意图

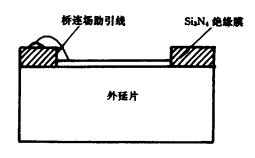

外延片放入真空系统并经过热烘烤和表面 热清洁之后便可进行蒸银制备肖特基结。TE 阴极要求银膜的厚度应小于 20nm, 而 Si₃N₄ 膜 的厚度通常大于 100nm, 所以经过第一次蒸银 后,场助电极并不能与阴极肖特基结实现连接, 如图 4 (a) 所示。因此必须蒸一层厚度大于 100nm 的银膜, 而这层银膜又不允许完全覆盖 有源区,只要与有源区边缘交叠 0.5~1mm 即 可。所以,在第二次蒸银时,必须掩盖大部分 有源区, 只暴露小于 1mm 的边缘, 这可通过调 节掩模板来实现。经过第二次蒸银后, 场助电 极与有源区肖特基结便可连接起来,如图 4 (b) 所示。由于场助电极的连接是在肖特基结 制备后原位进行的,因而不必对表面进行第二 次热清洁, 从而彻底消除了肖特基结热退化现 象。

27

a 第一次蒸银后

b 第二次蒸银后 图 4 阴极结构

# 4 实验结果和结论

在肖特基结制备过程中,我们在真空室外 利用示波器对其特性进行了实时测量,图 5 (a)给出第一次蒸银后的测量结果,图中表明正 反特性一致, 击穿电压大于 10V, 说明此时测 得的是 Au/Si<sub>3</sub>N<sub>4</sub>/InP 结构特性,场助电极与肖 特基结还没有连接起来,进行第二次蒸银是必 要的。图 5 (b) 为第二次蒸银后的肖特基结整 流特性测量结果。显然,经过二次蒸银,我们 获得了良好整流特性的肖特基结,空穴的势垒 高度大于 0.7eV,反向击穿电压大于 10V,实验 证明经过热烘烤和表面热清洁之后,PECVD-Si<sub>3</sub>N<sub>4</sub> 膜仍具有良好的耐击穿特性。同时也说明 二次蒸银技术能够实现场助电极在真空系统内 的原位连接,并彻底解决了肖特基结热退化问 题。

采用 PECVD-Si<sub>3</sub>N<sub>4</sub> 绝缘膜和多次蒸银技 术还具有更重要的意义。如果在外延片放入真 空系统之前,通过真空扩散焊接技术与双近贴 象管的基座粘接起来(该实验我们已在实验室 内完成),并在超高真空激活系统中安装转移铟

封机构, 那么, 在激活完成后便可以立即进行 冷压铟封,从而实现 TE 阴极器件的分离。可见 这个工艺为最终实现 TE 阴极器件的实用化打

下坚实的基础。

图 5 Ag/p-InP 肖特基结 I-V 特性

感谢西安电子科技大学微电子研究所杨银 堂在制备 PECVD-Si<sub>3</sub>N<sub>4</sub> 膜时给予的大力帮助。

## 考 文 献

- 1 Willardson R K, Beer A C. Semiconductors and Semimetals, 1981: 15:246~257

- 2 Bell R L, James L N, Moon R L. Appl Phys Lett, 1974; 25 (11) : 645~646

- 3 Escher J S, Bell R L, Grogrey P E et al. IEEE Transaction Electron Devices, 1980; 27 (7) : 1244~1250

- 4 Escher J S, Grogrey P E, Hyder S B et al. IEEE Electron Device Letters, 1981; 2 (5) : 123~125

- 5 李相民, 侯洵, 王存让, 程军, 张功力. 光子学报, 1994, 23 (3) : 262~267

- 6 李相民,王存让,程军,侯洵,刘英.光子学报,1994;23 (2) : 139~144

(收稿日期 19950103)

半导体技术 1995年8月第4期

28