文章编号: 1672-8785(2009)03-0007-11

# 阵列式日盲紫外成像 CMOS 读出集成电路 及凸点连接的制作

李高明 张景文 侯 洵 (西安交通大学电信学院物理电子专业, 陕西西安 710049)

摘 要: 可以广泛应用于军事和工农业生产上的 CMOS 紫外焦平面阵列 (UVFPA) 是近年来比较热门的研究课题。它可以比较容易地实现日盲式紫外探测和可见光盲式紫外探测。但在 CMOS UVFPA 的研制中,读出集成电路 (ROIC) 成了制约其发展的很重要的一环。 ROIC 芯片是实现探测器的信号输出的重要部件。混成式 CMOS UVFPA 要借助于先进的微电子封装工艺将 ROIC 与探测器阵列集成在一起。其中则需要制备用于高密度、高精确度互连的阵列凸点。我们通过蒸发结合光刻法和电镀法分别制备了线度为 30μm×30μm 的 16×16 凸点阵列。并对两种制备方法做了比较,在分析了制作的凸点的质量后,认为经过改进的蒸发结合光刻法可以制作高质量的阵列凸点。

**关键词**: 紫外焦平面阵列; 读出电路芯片; 封装键合工艺; 阵列凸点; 蒸发结合光刻法; 电镀结合光刻法

中图分类号: TN2 文献标识码: A

# CMOS ROIC for Solar-blind UVFPA and Preparation of Bump Interconnection

LI Gao-ming, ZHANG Jing-wen, HOU Xun

(Institute of Electronic and Information Engineering, Xi'an Jiaotong University, Xi'an 710049, China)

Abstract: The CMOS UVFPA which can be widely used in military, industry and agriculture has become a hot research subject in recent years. With the CMOS UVFPA, the solar-blind UV detection and visible light-blind detection can be implemented easily. However, in the development of the CMOS UVFPA, the Read Out Integrated Circuit (ROIC) is a very important restriction. The ROIC chip is an important part to implement signal output from detectors. For a hybrid CMOS UVFPA, its ROIC chip and detector array can be integrated with each other only by using the advanced microelectronic encapsulation process. In the integration process, a high density and high precision interconnection bump array should be fabricated. In this paper, the  $16\times16$  bump arrays with the bump size of  $30\mu m\times30\mu m$  are fabricated respectively by using a evaporation plus lithography method and a electroplating method. The analysis of the quality of the bumps fabricated by using these two methods shows that the improved evaporation plus lithography method can be used to fabricate bumps with high quality.

**Key words:** UVFPA, ROIC, encapsulation and bonding, array bump, evaporation and lithography method, electroplating and lithography method

收稿日期: 2008-09-16

基金项目: 国家自然科学基金 (60876042-F040305)、陕西省科技攻关项目 (2005K04-G6)

作者简介:李高明 (1986-), 男,湖南衡东人,西安交通大学电信学院物理电子学专业在读硕士研究生。研究方向为 ZnO 光电功能器件及紫外探测器。 Email: john.lee@stu.xjtu.edu.cn

# 1 引言

以光电效应为基础的光电探测器狭义地可分为光电导探测器和光伏探测器。光电导器件是在光作用于材料后形成光生载流子使材料电导率发生变化,从而实现光电转换的器件。光伏器件是光作用于结型材料产生非平衡少子进而产生结电压从而实现光电转换的器件。其本质都是光同固体相互作用产生电子或空穴这些光生载流子。随着光电器件朝集成化、小型化的方向发展,阵列化的光电探测器则成了具有成像功能的光电成像器件。当然也存在利用光电发射体加上电子束扫描偏转系统或称为电子光学系统的光电变像管的一类成像器件。

目前研究得比较热的焦平面成像阵列 (FPA) 即属于上述阵列式成像器件。近年来,由于 CMOS 集成电路芯片的飞速发展, CMOS 成像器件已能够很好地与后端的集成电路芯片兼容并实现小型化。 FPA 的大致原理是使光电探测器阵列位于像方的焦平面上,从而对被聚焦成极小的光斑进行光电转换,最后达到成像的目的。

在 FPA 研究中, 最常见的是红外 FPA。早期 的红外焦平面成像阵列还需要致冷,它们大多选 用 InSb(锑化铟) 和 HgCdTe (碲镉汞) 材料制作。 而非致冷的 IRFPA 则需要用到热释电焦平面技 术、微测辐射热计焦平面技术以及热电堆焦平面 技术。 UV FPA 较 IR FPA 研究起步稍晚, 且技 术没有其成熟。它采用的材料大多为 AlGaN 和 ZnMgO 等掺入其它元素的化合物半导体材料。 通过改变材料中各元素的比例, 可改变材料的 禁带宽度, 从而改变探测器响应范围的截止波 长。由于自然界中的一切物体均可以对外辐射 红外线, 而紫外线则除了人工制造的紫外光源 外仅有太阳能对外辐射紫外线。所以用 UVFPA 更容易实现日盲式和可见光盲式探测, 而不容 易受到环境的干扰。这也就使得 UVFPA 在军事 和工农业生产上具有更为重要的应用价值。

# 2 紫外焦平面成像阵列

我们用来制作 UVFPA 的材料是一种化合物 半导体材料。在化合物半导体材料中,较实用的 有III - V族、II - VI族、IV - VI族以及IV - IV族等二元化合物半导体和少量的三元化合物半导体。III - Vi族化合物中的 GaN 和 II - VI族化合物中的 ZnO 是做 UVFPA 研究时用的比较多的材料。而 ZnO 作为一种新兴的化合物半导体材料,有着诸多优于 GaN 的优良性能,近年来人们对其研究得比较热。 ZnO 具有纤锌矿的晶格结构,直接带隙为 3.2eV,属于宽禁带材料。由于禁带宽度决定本征吸收波长进而决定探测器的响应波长,宽禁带便意味着本征吸收的波长位于紫外波段,恰好可以实现我们所需要的紫外探测成像。

ZnO 材料成本低,易于制备,而且无毒,具有很好的热稳定性和化学稳定性,并且具有较高的激子束缚能、较大的光电耦合系数、较高的透光率和较小的介电常数。由于 ZnO 材料存在填隙的锌原子和氧空位,它们均能提供自由电子,因此属于 N 型点缺陷。而制得的 ZnO 大多是 N 型的。这也是我们常说的 ZnO 材料的高度自补偿作用。 ZnO 薄膜的制备方法有很多,其中有溅射法、喷雾热解法、化学气相沉积法、溶胶凝胶法和脉冲激光沉积法。我们在实验中选用的是射频磁控溅射法。用溅射法制得的 ZnO 薄膜的附着力较好且膜比较致密。应当说这是一种成膜质量较好的制备方法。

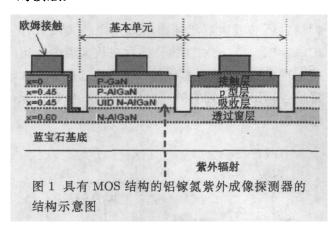

紫外成像系统主要可以分为五个部分: 信 号探测部分、信号传输部分、信号处理部分、信 号存储部分和信号显示部分。其中最为关键和 重要的应当是信号探测部分和信号传输部分。 信号探测部分即我们制作的 UVFPA。其阵列单 元是如图 1 所示的一个 PIN 型光电探测器。背 光式探测器一般做在一个对所探测波段的光透 明的基底上。基底通常选用对紫外光透明的蓝 宝石基底。典型的结构探测器有五层,它们分别 是应力缓冲层、透过窗层、吸收层、P型层和 P 型欧姆接触层。应力缓冲层用于减小蓝宝石衬 底和其上的 ZnO 薄膜的应力, 以使 ZnO 薄膜的 附着力更大。透过窗层相当于一个滤光膜, 它将 截止波长短波限以下的光全部吸收, 只允许此 波长以上的光波通过, 因此它的带隙决定了响 应波段的短波方向的截止波长。一般情况下,该 层的掺杂浓度较大。吸收层是进行光电转换的

有源层,它吸收光子的能量,使价带上的电子跃迁到导带上形成自由载流子。产生的自由载流子会在由外加偏压形成的电场下运动,形成相应的电信号。它的带隙决定了长波方向的截止波长。 P型层与吸收层会形成 P-N 结的结构, P-N 结中央会形成一个耗尽层,耗尽层的的海域时间有影响,进而也会对探测器的响应时间产生影响。欧姆接触层用于将探测器产生的信号输出给后面的读出电路,因此它一般被做成接触电阻小、易实现电连接的欧姆接触。

信号传输部分中最重要的是读出电路。读 出电路是用 CMOS 工艺制作的集成电路芯片, 称为 CMOS ROIC。读出电路芯片在尺寸上同探 测器阵列相仿。与探测器之间的电连接是由凸 点来实现的。由于探测器成像阵列通常具有很 多单元,如 128×128 元或者 256×256 元, 所以必 须采取高密度和高精确度的凸点连接。在时序 逻辑的控制下,读出电路芯片会对探测器进行 逐行扫描, 将探测器输出端的信号读出。它是典 型的集数字与模拟于一身的混合集成电路。通 过读出电路的传输转换, 可实现一个空间上二 维的信号到时间上一维的信号的转换。之后, 读 出电路芯片再把信号传输给下一级信号处理部 分。读出电路芯片的重大作用体现在它实现了 在平方毫米量级大小上的探测器的电信号的高 速和准确读出。ROIC 的噪声对系统整体的噪声 有较大的影响。

信号处理部分主要用于实现 A/D 转换、坏元的替代、图形的校正, 使输出的信号变成标准

的视频信号,以供信号显示部分直接显示。由于信号处理部分需要在一定的程序的控制下完成相应的任务并且由于信号处理部分中的各个小部分的处理速度不一致,需要对被处理的数据做暂时的存储以作为缓冲。这就需要用信号存储系统来存储传输的数据和存放信号处理部分所需要的程序和指令。信号显示部分的功能是对探测信号进行可视化输出,通常用一台显示器就可以了。它实际上将时间上的一维信号重新又还原成了空间上的二维信号。

## **3 ROIC** 的介绍

#### 3.1 ROIC 的研究现状

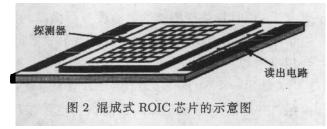

ROIC 的研究可追溯到上世纪 70 年代, 当 时研制的 ROIC 主要是用于红外成像系统的。从 ROIC 的发展史来看,它经过了一个由单片式向 混成式,由单一的 NMOS 或 PMOS 到 CMOS 的 发展过程。 混成式 ROIC 的出现归功于半导体技 术封装工艺中的凸点连接技术。适合于高密度 互连的阵列凸点可以将探测器和 ROIC 集成在一 起。这样相比于将探测器和读出电路合二为一做 成一个结构的单片式器件, 混成式器件能较好地 解决困扰单片式结构的电场问题。 混成式 ROIC 芯片如图 2 所示。单片式器件中因为有 CCD 结 构起多路传输器作用, 所以不能加过高的电压, 以免产生过强的电场。在没有使用 CMOS 之前, 人们只使用单纯的 NMOS 和 PMOS, 因为外延 层的厚度和一些加工工艺达不到实现 CMOS 的 要求。这样就限制了 ROIC 电路的性能。后来出 现的 CMOS ROIC 在很多性能指标上都得到了改

美国对 ROIC 的研究起步较早,当时的航空航天部门和一些军事研究单位对用于红外成像 FPA 的 ROIC 研究得很热。如美国休斯飞机公司的圣巴巴拉研究中心曾在上世纪研制出 32×32元和 45×90元的 Si: In 焦平面阵列。我国的 ROIC

INFRARED (MONTHLY) / VOL.30, No.3, MAR 2009

研究则起步稍晚,目前从事 ROIC 研究的单位有重庆大学、重庆邮电大学、中国电子科技集团公司第四十四研究所等。重庆大学近来研制出了128×128 元的硅基 ROIC 芯片。 ROIC 对于整个成像系统有很大的制约,其质量的好坏对系统的成像质量有很大的影响。

#### 3.2 ROIC 的种类及各自的特点

ROIC 以其前置放大器实现的电路来分,可分为直接注入型 (DI)、每个像元带源跟随器型 (SFD)、电阻负载栅极调制型 (RL)、反馈增强直接注入型 (FEDI)、电源反射镜栅极调制型 (CM)以及电容反馈互导放大器型 (CTIA)。直接注入型 (DI) 的原理非常简单,就是由探测器输出电流对积分电容进行充电。积分电容可以调整放大的增益。由于结构简单,所以占用的芯片面积也很小。

SFD 相比直接注入型,增加了一个复位晶体管和一个源跟随器。它也是对探测器的输出电流进行直接积分的。而且由于复位晶体管的存在,它还可以对探测器的输出端进行复位。其主要噪声是 KTC 噪声和 MOSFET 的 1/f 噪声以及通道的热噪声。它适合于在辐照背景比较低的情况下使用。

RL 比 SFD 多了一个负载电阻,它可以调制输出的源跟随器上的栅电压。它的 1/f 噪声较小,适合在探测器输出电流较大即背景辐照较强时使用。

FEDI 相比 DI 使用了一个反相放大器, 这是用来提高注入效率的。它的响应线性范围变得更大了, 而且也使探测器的灵敏度有所提高。但由于增加了一个反相放大器, 其功耗和面积也会相应增加。

CM 用一个 MOSFET 取代了 RL 型中的负载 电阻,并通过电流镜把探测器的输出电流按比 例传递给积分电容。它也适合于背景辐照较强 的情况。它的缺点是线性度和稳定性不好。

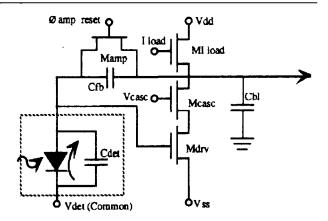

CTIA 实质上是一种复位积分器,它也是由复位管、积分电容、放大器和一个防止自激振荡的电容构成的。它的电路原理图如图 3 所示。

图 3 电容反馈互导放大型 ROIC 电路的原理图

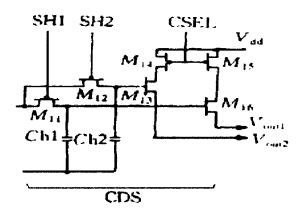

为了减小噪声和偏移,增大动态范围,人们通常还在放大器的输出端加一个相关双取样(CDS)电路。它分别在积分前后在放大器的输出端进行采样,并由电容保持,然后通过差分放大将信号输出给后续的处理电路。 CDS 电路的原理图如图 4 所示。

图 4 相关双取样电路的原理图

由于晶体管数量较多而且其性能较其它类型好,尤其是它具有噪声低、探测器偏压恒定、积分电容可调、线性度好、均匀性好以及动态范围大等优点,所以目前的 ROIC 大多是这种 CTIA 读出电路。

#### 3.3 ROIC 的性能指标

ROIC 的性能指标前面已经提到过,包括噪声、线性度、均匀性、温度稳定性、动态范围、带宽、芯片面积和功耗,而其中最重要的是噪声。很多关于成像 FPA 的研究均发现,整个成像系统的噪声的主要贡献者就是 ROIC。所以在设计和制造 ROIC 的过程中,主要考虑的是如何减小电路的噪声。有时甚至会不惜以牺牲其它的性

能指标为代价。以 CTIA 型 ROIC 为例、为了获 得较小的噪声, 不得不采用晶体管数量较多的 差分放大器,并且还要附加 CDS 电路。这就是 以面积和功耗为代价来换取好的线性度和均匀 性的。 更重要的是好的噪声特性。 在诸多的性能 指标中,我们只能选择一个折衷的方案,以使大 多数性能指标能够得到优化, 尤其是那些比较 重要的指标。对 ROIC 有影响的噪声主要有 KTC 噪声、1/f 噪声以及热噪声。一般、加入反馈有 利于改善噪声特性,减小工作的暗电流和提高工 作频率可降低 1/f 噪声, 而降低工作温度则可降 低热噪声。同时,加入反馈还可以改善线性度、 均匀性和稳定性。而改善 CMOS 的加工工艺, 则可以提高 ROIC 的均匀性。优化电路的设计, 减小电路中晶体管的数量,则可以减小芯片面 积,降低功耗,甚至降低工艺的复杂程度,从而 降低芯片的成本。

# 4 微电子封装工艺及凸点连接

#### 4.1 微电子封装工艺的发展历程

前面提到过凸点连接技术对 ROIC 的发展起了巨大的作用。而提到凸点连接技术就不得不提微电子封装键合工艺了。封装是为了保护芯片使其免受环境的不良影响,实现电气连接。封装不仅可以为芯片提供物理支撑,而且还便于芯片散热。随着集成电路芯片的集成度工艺体度,集成电路的封装键合工艺格度,集成电路改进。其实,严格地说,封装的概念有两层含义:第一层是说把面积极小、极脆弱的管芯封装成具有陶瓷或塑料基底的集成电路块;第二层则是说将封装型的角、放电路块与其它部件进行连接,使其容入到测器上形成混成式 FPA 的,这应当属于第二层含义上的封装。

传统的封装工艺分为背面减薄、分片、装架和引线键合四步。背面减薄是通过机械的方法将硅片的背部磨去一部分,使得硅片的厚度在200μm到500μm范围内。硅片的厚度变薄,散热会更加容易,而且自身的重量也会随之减小,分

片也会因为背面减薄而变得更加容易。分片是将硅圆片上的若干管芯切割下来。分片之后就是装架,即将切好的管芯装入引线架或装在衬底上,通常这一步会用到环氧树脂、共晶焊或者玻璃焊料。最后一步是引线键合,即用引线将框架上或是衬底上的电极与硅片上的金属压点转起来,实现电气上的连通。键合线通常是铝线或金线,其直径在 25 µm 到 75 µm 之间。键合的种类有热压键合、超声键合和热超声球键合。但随着集成电路的发展,集成度越来越高,电路越来越复杂,其输入输出的引脚和压点也越来越多。仅靠利用单纯键合的传统封装工艺显然已无法达到高性能、高集成度 IC 芯片的要求。这时一些先进的封装键合工艺就应运而生了。

#### 4.2 微电子封装工艺的种类

传统的封装形式包括 DIP 双列直插式、SIP 单列直插式、 TSOP 薄小型封装、 QFP 四边形 扁平封装、 PLCC 塑封电极芯片载体、 PGA 针 栅阵列、应用了比较先进的 SMT 技术即表面贴 装技术的和已经渐露先进封装技术雏形的无引 线芯片载体技术。其中,管脚密度比较高的属 QFP 四边形扁平封装技术, 其最小管脚间距为 300 µm。而先进的封装技术则是以无引线的倒 装芯片技术为代表的一系列适合于高密度、高 可靠性互连的新型封装工艺技术, 如 BGA 球栅 阵列技术、COB 板上芯片技术、TAB 卷带式自 动键合技术、 MCM 多芯片模块、 CSP 芯片尺 寸封装、WLP 圆片级封装以及倒装芯片技术。 其中的倒装芯片技术是将芯片含有键合压点的 有源面倒向衬底基片, 通过高密度的阵列凸点 来实现电气上的互连。这种互连方式对芯片表 面积作了很好的利用, 不再像传统的封装键合 工艺那样,只对芯片的四周加以利用。这样,芯 片输入输出的引脚压点也就大大增加了。它的 出现其实反映了封装键合从有引线到无引线、 从只在芯片四周制作压点到在整个芯片的表面 均制作压点、从低的互连密度到高的互连密度 的发展趋势。其它的先进封装键合工艺也是在 降低成本、简化工艺流程、提高互连的可靠性以 及增加互连密度等方面对传统的封装键合工艺 进行改进而发展成的。

#### 4.3 凸点连接

倒装芯片技术中很重要的一步就是制作凸点。凸点工艺最早是由 IBM 公司于上世纪 60 年代为了解决高密度互连问题而开发出来的。当时的凸点成分是锡铅焊料。凸点的直径为 250 μ m,间距为 100 μm。通过凸点将芯片与陶瓷基座连接在一起,使得芯片的压焊点与输入输出管脚之间实现电气的连通。 IBM 公司开发的这一凸点工艺又被称为 C4 凸点工艺, C4 指的是可调整的芯片支撑工艺。

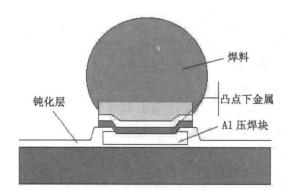

凸点的外形看上去像是一个球冠,如图 5 所示。

图 5 球冠状凸点的示意图

其实,除了球冠状的凸点外,也有柱状的凸 点。 凸点的外形主要取决于制备凸点时光刻胶的 厚度。如果光刻胶厚并且去胶后不进行回流的 话, 凸点的形状则为柱状。 凸点的结构包括凸点 和凸点下金属。凸点的材料可以是金、镍、铜等 非焊料金属,也可以是锡铅、锡银、锡银铜、金 锡、铟等焊料金属, 甚至还可以是一些导电聚合 物材料。我们在实验中是使用低熔点金属铟来 制备凸点的。 铟是第五周期第Ⅲ主族的元素, 它 是一种光亮、质软、银白色的稀有金属。由于比 较稀少, 所以价格昂贵。它的熔点为 156.6 ℃, 沸点为 2080 ℃, 密度为 7.31g/cm³ (22 ℃), 电阻 率为  $2.2\mu\Omega$ cm (22 °C)。由于其熔点很低,所以在 加热加压后能很好地实现电路连接。凸点下金 属材料是镍、金、钛、铜、钛钨等金属,可根据 不同的凸点材料选择不同的凸点下金属材料。 我们制作铟凸点使用的是钛和铜。凸点下金属 层的主要作用是增加附着和扩散阻挡。凸点制 备完后, 在对芯片与基底进行互连时, 还要进行 对准,之后还要加压加热,让凸点金属与基底上的键合压点充分接触,从而使互连更加稳定可靠。由于凸点的尺寸很小且凸点间的间距很小,所以对准尤其需要注意,以防止因凸点错位而出现误连。

凸点的制备方法有蒸发结合光刻法、电镀法、丝网印刷法和喷射法。其中丝网印刷法使用的设备简单,成本低,但由于制作的凸点精度不高,不能满足实验的需要。而喷射法使用的设备昂贵,并且适合于大规模生产。因此虽然其制备的凸点精度高,质量好,并且制备周期短,但我们仍然也不选用。实验中,我们选用的是蒸发结合光刻法和电镀法。我们用上述两种方法在硅片上制备了线度为 30 μm×30 μm 的 16×16 凸点阵列,并比较了用两种方法制备的凸点的质量,分析了两种方法的优缺点。两种方法的具体步骤将在下面作详细介绍。

# 5 凸点的实验室制备

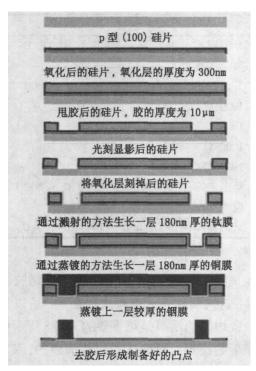

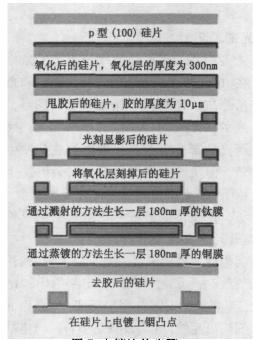

用于制备凸点的电镀法和蒸发结合光刻法的前面的步骤是相同的,其区别主要在进行了蒸发镀膜之后,即制作完凸点下金属的铜膜以后。两种方法的步骤如图 6 和图 7 所示。蒸发结合光刻法是在做完凸点下金属 Cu 膜后,再继续蒸镀铟即凸点金属材料,最后再进行去胶,从而完成凸点的制作的。电镀法是在制作完凸点下金属 Cu 膜后,直接去胶,再通过电镀的方法在凸点下金属上镀铟凸点的。

#### 5.1 氧化工艺

我们选用的衬底是 P型 (100) 硅片。在氧化前,我们先对硅片进行清洗。这主要是借助于 KQ3200B 型超声波清洗器进行的。先将硅片放在清洁的烧杯中,加入约 30ml 的丙酮,然后将烧杯放入超声波清洗器中。在超声的振动下,表面上的沾污物即会去除。在超声清洗器中清洗的时间为 10min。之后,将烧杯取出,倒去废液,加入约 30ml 的酒精溶液,再在超声波清洗器中清洗 10 min。最后再用约 30ml 的去离子水借助超声清洗器清洗 10min。由于硅片表面可能还存在自然氧化层,还需要放在氢氟酸中去除表面的二氧化硅。氢氟酸会腐蚀玻璃,需要用塑料烧杯来盛装。清洗完后,可用氦气将硅片表面

吹干.

图 6 蒸发结合光刻法的步骤

氧化可分为干法氧化 (简称干氧) 和湿法氧化 (简称湿氧) 两种。用干氧制备的氧化膜的质量比用湿氧制备的氧化膜的好,但湿氧的速率更快。氧化速率随时间的变化是接近抛物线型的。影响氧化速率的因素有很多,如温度、压强、晶向、掺杂浓度以及氧化方式。掌握氧化速率的变化规律对于通过膜厚来确定氧化时间是很重要的。氧化的模型有 Deal-Grove 模型,它把氧化分为两个阶段。第一个阶段为线性阶段,它主要是描述初始至氧化层厚度为 15nm 时的这一段时间。这一阶段的氧化速率主要受反应速率控制,即反应速率制约着氧化的速率。这时,氧化层厚度的表达式为

$$X = \left(\frac{B}{A}\right)t\tag{1}$$

式中, X 为氧化层厚度, A 和 B 为常数, t 为时间。

从式中可以看出这时的厚度是随时间线性变化的。但这一阶段持续的时间很短,很快就进入了第二个阶段。第二个阶段是抛物线阶段,它

主要是描述从氧化层厚度为 15nm 到之后的这一段时间。这一阶段的氧化速率主要受到氧分子扩散速率的制约。随着厚度的增加,氧分子扩散 到氧硅界面所需的时间越来越多,因此氧化的 速率也就越来越慢。此时,氧化层厚度的表达式 为

$$X = \sqrt{Bt} \tag{2}$$

式中, X 为氧化层厚度, B 为常数, t 为时间。

从式 (2) 可以看出, 这时的厚度是随时间呈 抛物线型变化的。这一阶段占据了整个氧化过程的绝大多数时间,

图 7 电镀法的步骤

我们在实验中是使用 HDC-8000A 型扩散炉来实施干氧的,该扩散炉如图 14 所示。扩散炉的氧化工艺由工艺菜单控制。实验人员只需要打开气瓶的阀门、放片和取片就行。表 1 列出了我们使用的工艺菜单。

经过氧化的硅片表面呈紫色,由于硅片的颜色会随硅片表面的氧化层厚度呈周期性变化。根据手册,我们粗略地估计其厚度为 300nm 左右.后来我们使用椭偏仪进行了膜厚的测量,测量结果证实了我们的估计.氧化层在实验中主要起钝化层的作用,它可以保护下层的硅片不受后续工艺的影响。

| 序号 | 操作 | 时间                | 气体流量        | 温度                              |

|----|----|-------------------|-------------|---------------------------------|

| 1  | 升温 | 2h40min           | 氮气: 200sccm | 升温斜率: 5 ℃ /min , 20 ℃ ~ 800 ℃   |

| 2  | 保持 | 3min              | 氦气: 200sccm | 放片 800 ℃                        |

| 3  | 升温 | $40 \min$         | 氦气: 200sccm | 升温斜率: 5 ℃ /min , 800 ℃ ~ 1000 ℃ |

| 4  | 保持 | 23min             | 氧气: 200sccm | 1000 °C                         |

| 5  | 保持 | 7h                | 氧气: 200sccm | 1000 ℃,氧化                       |

| 6  | 保持 | 23 min            | 氦气: 200sccm | 1000 ℃                          |

| 7  | 保持 | $20 \mathrm{min}$ | 氦气: 200sccm | 1000 ℃                          |

| 8  | 降温 | $40 \mathrm{min}$ | 氦气: 200sccm | 降温斜率: 5 ℃ /min , 1000 ℃ ~ 800 ℃ |

| 9  | 保持 | 5 min             | 氦气: 200sccm | 取片 800 ℃ .                      |

| 10 | 降温 | 5h                | 不通气体        | 降温斜率: 5 ℃ /min , 800 ℃ ~ 20 ℃   |

表1 氧化工艺的工艺菜单

#### 5.2 光刻工艺

光刻中我们采用的是厚胶工艺,光刻胶的厚度在10µm左右。光刻胶可分为正胶和负胶。正胶所形成的图形同于掩膜版上的图形,而负胶形成的图形则与掩膜版的图形相反。因为正胶中曝光的部分会与显影液中的成分发生反应而溶解,而负胶中曝光的部分则会因发生交联反应留下,其它部分则会溶解在显影液中。一般情况下,正胶形成的图形在质量上优于负胶形成的图形。

我们在实验中采用的是正胶工艺, 所用的正 性光刻胶是北京化学试剂厂出品的 BP218 型光 刻胶。 显影液为 BP212 型显影液, 也是由北京化 学试剂厂出品的。光刻设备是中科院光电技术研 究所研制的 URE-2000A 型紫外深度光刻机。光刻 中采用的是 I 线紫外曝光源和接触式光刻, 紫外 光源的波长为 365nm。光刻的具体步骤如下: ① 甩胶, 使用的甩胶机是 CHEMAT TECHNOLOGY SPIN-COATER KW4-A 型甩胶机。 甩胶的时间为 60s, 甩胶机的转速为 3000RPM; ②前烘, 使用的 是 CT HOT PLATE MODEL KW-4AH 型仪器。 烘 胶的时间为 5min, 烘胶的温度为 90 ℃; ③重复 1和2步骤十次; ④曝光, 需要对光强进行测定 并对曝光时间进行设定,在光强为 1.4mW/cm2 时, 曝光的时间定为 6667s 比较合适; ③显影, 将曝光后的硅片放在显影液中晃动, 观察去胶 情况。对于厚胶,显影的时间定为 5min 左右比 较合适。表2所示为厚胶光刻剂量的实验数据。

光刻后的硅片用肉眼就能发现光刻胶的不 均匀性。这对后续工艺有很大的影响。所以甩胶 达到一致均匀的结果是很重要的。图 8 所示为在 显微镜下的图形,图形还是比较清晰的。

表 2 厚胶所用光刻剂量的实验数据

| 序号 | 光强<br>(mW/cm²) | 曝光时间<br>(s) | 曝光剂量<br>(J/cm²) | 效果  |

|----|----------------|-------------|-----------------|-----|

| 1  | 1.5            | 335         | 0.5             | 不足  |

| 2  | 1.4            | 572         | 0.8             | 不足  |

| 3  | 1.4            | 714         | 1.0             | 不足  |

| 4  | 1.4            | 2857        | 4.0             | 不足  |

| 5  | 1.4            | 4286        | 6.0             | 不足  |

| 6  | 1.5            | 6673        | 10.0            | 略不足 |

| 7  | 1.4            | 8571        | 12.0            | 过量  |

#### 5.3 蚀刻工艺

蚀刻可分为干法蚀刻和湿法腐蚀。干法蚀刻的原理较简单,它是通过射频电源使处在一定真空度下的气体产生辉光放电形成等离子体,然后利用电离的正离子轰击掉样片上不需要的部分。干法蚀刻又可以分为电子回旋加速振荡蚀刻、感应耦合等离子体蚀刻、反应离子蚀刻等。蚀刻也不完全是物理作用,如果过程中发生了化学反应,就还应当包括化学作用。我们是使用 RIE-3 型反应离子蚀刻机、通过三氟甲烷气体对硅片上的二氧化硅进行蚀刻的。蚀刻的条件是:通入的三氟甲烷气体的流量为 40sccm,真空室内的压强保持在 3Pa,射频电源的功率为

图 8 光刻后的硅片在显微镜下的图形

300W。蚀刻的速率为 60nm/min。我们的蚀刻时间为 5min。由于蚀刻机长时间不使用,蚀刻速率可能会略偏小一点,而蚀刻的时间就会略长一点。

蚀刻后,硅片表面有光刻胶的地方由于受到高能离子的轰击出现了很多泡,光刻胶失去了大量水分,变得很干。没有光刻胶的地方由于氧化层已经被蚀刻掉,原有的紫色已消失不见了。我们用万用表测量了其电阻,结果显示电阻已变得很小,说明暴露出来的氧化层确实已经被蚀刻掉了。

#### 5.4 溅射工艺

溅射的原理与蚀刻很相似,也是利用射频电源使处在一定真空度下的气体发生辉光放电,进而产生带有较高能量的正离子去轰击靶材,使靶材原子或原子团落到要沉积的基片上。与蚀刻不同的是,溅射时基片是同外加电源的正极相连的,而蚀刻时基片是同外加电源的负极相连的。溅射常用的气体是氩气,因为氩离子的溅射产额较大。

我们在实验中使用的是 JPG300 型高真空单 靶磁控溅射设备。溅射的条件为:气压为 1Pa~1.2Pa,射频源功率为 100W,频率为 13.56MHz,溅射时通入的氩气的流量为 60sccm,溅射的时间为 1h48min。在正式溅射前,先进行 20min 的预溅射。使用的靶是直径为 75mm、厚度为 5mm、纯度为 99.99% 的高纯钛靶。

溅射完后, 硅片表面上有一层蓝紫色的金属膜层。 溅射的钛膜的厚度为 180nm。 这便是我们所需要的第一层凸点下金属。

# 5.5 蒸发镀膜工艺

蒸发镀膜工艺的原理是非常简单的,它通过在蒸发源上加上较大的电流,放出大量的热使得位于其中的金属熔化并蒸发,从而在基片上镀上需要的膜层。因此作为蒸发源的金属必须是高熔点的金属,如钨、钼等。

我们在实验中蒸镀的金属是铜,我们用的蒸发源是一个用钼片加工成的长为 50mm、宽为 3mm、厚度为 0.5mm 的钼舟。蒸镀时的本底真空度为 8×10<sup>-4</sup>Pa,蒸发用电流为 70A ~ 80A。希望蒸镀的铜膜的厚度为 180m。

#### 5.6 电镀工艺

电镀工艺的原理简单,就是将被镀基片放在含有所要镀的金属的盐溶液中,将其与直流电源的负极相连,并用石墨或者该种金属与直流电源的正极相连。正负离子作为载流子在电解质溶液中会分别向不同的电极运动。金属离子运动到基片上发生电子还原反应,变成金属单质,并逐渐形成金属薄膜。电镀时,要求被镀基片具有良好的导电性。电镀对电解质溶液浓度和 pH 值的要求很高,它们的稳定性对成膜的一致性和均匀性有很大的影响。

在电镀过程中,我们是在硅片上制成凸点下金属层之后进行去胶的。去胶后除了凸点下金属层形成的图形外,硅片上的其它部分均是氧化层,所以硅片上能导电的就只剩下将要制作凸点的部分了。当将硅片置于电解质溶液中进行电镀时,就只会在将要制作凸点的地方镀上金属。

我们在电镀铟凸点时查阅了《电镀工艺手

INFRARED (MONTHLY) / Vol.30, No.3, MAR 2009

册》,镀铟的条件为: 硫酸铟溶液的浓度为  $20 \sim 45 g/L$ ,硫酸钠溶液, 浓度为  $0 \sim 10 g/L$ , pH 值的范围为  $2 \sim 2.7$ ,电流密度为  $0.5 \sim 5 A/dm^2$ ,温度为室温。用铟作阳极,用被镀的硅片作阴极。电镀的时间要根据电流密度与电镀速率来确定。

#### 5.7 去胶及凸点的观测

在利用蒸发结合光刻法制备凸点时,最后一步是去胶。去胶是利用丙酮可以将光刻胶溶解这一特性,将光刻胶连同不需要的金属膜层去除。由于铟的熔点很低,所以镀好铟凸点后不能在超声波清洗器中用超声波辅助去胶,不然会导致铟凸点熔化。但如果采用电镀法,由于电镀铟是去胶之后进行的,可以先用超声波辅助去胶,之后再进行电镀。

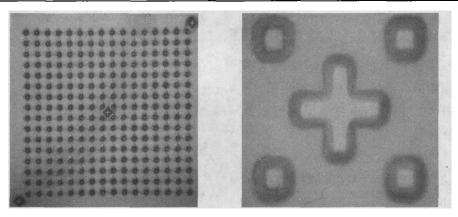

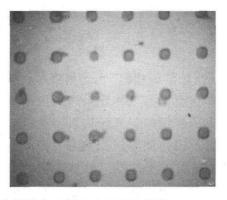

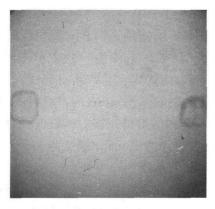

在采用蒸发结合光刻法的硅片上可以用肉眼观察到一些细小的凸点。不过也可以看出去胶是不完全的,凸点之间有许多应该去掉的部分却没有去掉。结果导致许多凸点连在了一起。采用电镀法的硅片虽然去胶去得很干净,但有些

希望留下的部分也被去掉了,这说明在光刻完后有些应该去掉的光刻胶没有被去掉。图 9 为在光学显微镜下观察到的用蒸发结合光刻法去胶后的硅片。图 10 为在光学显微镜下观察到的用电镀法去胶后的硅片。

## 6 结论

我们通过蒸发结合光刻法和电镀法分别制备了线度为 30μm×30μm 和 16×16 的阵列凸点。 用两种方法制备的凸点各有其优缺点。

用蒸发结合光刻法制作的凸点有交连成片的现象,凸点与凸点之间应该去掉的金属层没有去掉,这可能与凸点之间的距离太小,光刻胶不易去除有关。在去胶时,由于铟凸点的熔点较低,不能用超声波辅助去胶。

用电镀法制得的凸点与基底硅基片的附着不牢,有凸点脱落的现象。在某些应当有凸点的地方没有生长上凸点。并且由于电镀时溶液的浓度和 pH 值是时刻变化的,不易控制,因而制

图 9 在光学显微镜下观察到的用蒸发结合光刻法去胶后的硅片

图 10 在光学显微镜下观察到的用电镀法去胶后的硅片

得的凸点的一致性和均匀性不太好。

总结整个实验过程,我认为用蒸发结合光刻法是应当能制备出高质量的凸点的。但对光刻这一步骤要尤其注意,因为这一步对后续的步骤有很大的影响。这次实验结果不令人满意也和光刻有很大的关系,在涂胶后用肉眼可以观察出光刻胶有明显的不均匀性。这样会导了,而考些胶厚的地方没有去掉。若对光刻等其它步骤再加以改进,应当是能改善实验结果的。例如,通过提高甩胶的速度,应当可以改善涂胶的均匀性。以本次实验为基础,通过改进工艺步骤,应当是能够制作出高质量的、可用于高密度互连的阵列凸点的。

#### 参考文献

- M B Reine, A Hairston, P Lamarre, et al. Solar-blind AlGaN 256×256 p-i-n detectors and focal plane arrays [C]. Proc. of SPIE, 6119: 611901-1-1611901-15.

- [2] Ryan McClintock, Alireza Yasan, Kathryn Mayes, et al. Back-illuminated solar-blind photodetectors for imaging applications [C]. Proc. of SPIE, 5732: 175-184.

- [3] Paul Schreiber, Tuoc Danga, Thad Pickenpaugha, et al. Solar Blind UV Region and UV Detector Development Objectives [C]. SPIE, 3629: 230-248.

- [4] Mary J Hewitt, John L Vampola, Steve H Black, et al. Infrared readout electronics: a historical perspective [C]. SPIE, 2226: 108-119.

- [5] 袁祥辉, 吕果林, 黄友树, 等. 红外焦平面 CMOS 单元 读出电路 [J]. 半导体光电子, 1999, 20(2): 123-126.

- [6] 陈勇, 皮德富, 周士源, 等. 红外焦平面阵列 CMOS 读出集成电路的研制 [J]. 电子工程师, 2000(9): 39-41.

- [7] 刘豫东, 谭智敏, 钱志勇, 等. Pb/Sn 凸点的制备 [J]. 电子元件与材料, 2002(9): 4-5, 20.

- [8] 林小芹,朱大鵬,罗乐,等. 微尺寸 SnAg 凸点的制备 技术及其互连可靠性 [J]. **半导体学报**, 2008, **29**(1): 169-173.

- [9] 刘豫东, 谭智敏, 钱志勇, 等. 焊料凸点回流时的 桥接现象研究 [J]. 电子元件与材料, 2002(8): 1-3.

- [10] 彭昀鹏, 张景文, 侯洵. 平板电封装工程中的凸点实现及其在紫外焦平面成像阵列中的应用 [J]. **红外**, 2008, **29**(2): 14-25.

- [11] 罗驰, 练东. 电镀技术在凸点制备工艺中的应用 [J]. **微电子学**, 2006, **36**(4): 467-472.

- [12] 鲜飞. 微电子封装技术的发展趋势 [J]. **半导体行业**, 2005(4): 56-59.

- [13] 肖汉武. 芯片凸点技术发展动态 [J]. 电子产品世界, 2001(1): 78-79.

- [14] 杨建生. 倒装芯片封装技术的凸点、压焊及下填充 [J]. **半导体技术**, 2004, **29**(4): 35-37.

- [15] Michael Quirk, Julian Serda. Semiconductor Manufacturing Technology [M]. 韩郑生, 等. 北京: 电子工业出版社, 2004, 1版: 210-233.

# 简 讯

# 硅棒显示出红外超准直特性

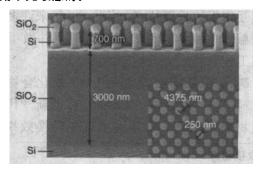

据《Laser Focus World》杂志报道,最近,美国麻省理工学院和美国宽网公司的科学家在一种由介电纳米棒构成的光子晶体板坏中进行了第一次超准直实验演示。所谓超准直,就是光的无衍射传播,它是利用光子晶体的特性在适合于集成光学互连的厘米级距离发射信号实现的。

麻省理工学院的研究人员在一块方形的 SO<sub>2</sub> 衬底上制备了大量半径为 125nm、高度为 700nm、间距为 437.5nm 的硅棒,这些硅棒都是为 1550nm 超准直波长设计的。为了实现折射率导引,这些硅棒与底下的衬底之间是用一层 3µm 厚的低折射率 SO<sub>2</sub> 隔开的。

研究人员将来自可调谐激光器的横磁偏振光通过

一根单模光纤射向该超准直器样品,该偏振光落在晶格顶部平面上的光斑大小为 2.5 µm. 散射光以 1550nm 波长从厚片侧面出现,并传播了长达 1000 个晶格周期或数百微米的距离. 因此,这种棒作为超准直器所呈现的灵敏度比类似的气孔型超准直器提高了六倍,说明它们是适用于光敏感的.

口高国龙

INFRARED (MONTHLY) / VOL.30, No.3, MAR 2009